IBM-Research-Projekt cloudFPGA

30.03.2022, 06:38 Uhr

Logikchips für die Hyperscaler-Cloud

Die Hyperscaler setzen in ihren Rechenzentren auf Standard-Hardware. Programmierbare und daher flexiblere Logikchips sind noch eher selten. Forscher von IBM Research Zurich haben ein Referenzdesign entwickelt und getestet.

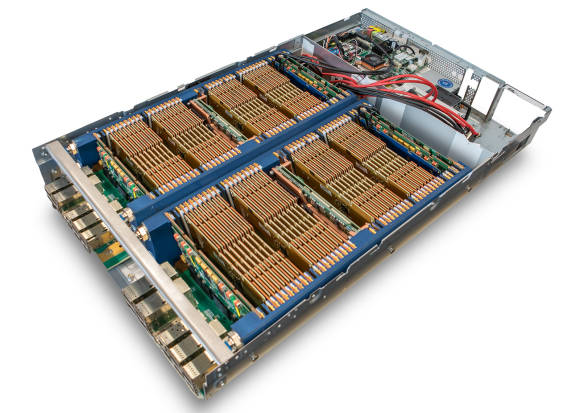

Für das cloudFPGA mit 64 Steckkarten wurde ein Standard-Servereinschub komplett neu entwickelt

(Quelle: IBM Research Zurich)

Milliardensummen investierten die beiden Halbleiter-Giganten AMD und Intel in den vergangenen Jahren in programmierbare Logikchips (Field Programmable Gate Arrays, FPGA). Intel übernahm 2015 den FPGA-Hersteller Altera für 16,7 Milliarden US-Dollar, Anfang Jahr schluckte AMD den Weltmarktführer Xilinx im Rahmen des grössten Zukaufs der Firmenhistorie für rund 35 Milliarden US-Dollar. Zum Vergleich: Für den Grafikchip-Spezialisten ATI waren im Jahr 2006 «nur» 5,6 Milliarden Dollar geflossen.

Während Intel die FPGA-Produktion in die Programmable Systems Group (PSG) einsortierte und damit bis anhin mässig erfolgreich war, hat AMD mit Xilinx nun Grosses vor: Die programmierbaren Logikchips sollen das Portfolio für Server und Rechenzentren erweitern. Die FPGAs kommen heute erst selten in Rechenzentren zum Einsatz – trotz ihrer hohen Flexibilität und Leistungsfähigkeit. Hinderungsgründe sind die im Vergleich zu CPUs und GPUs aufwendige Programmierung, die hohen Hardware-Kosten und die fehlende Steuerungs-Software. So kommen FPGAs in heutigen Rechenzentrums-Szenarien ausschliesslich in Kombination mit CPUs oder GPUs zum Einsatz: Die Logikchips übernehmen dann spezielle Aufgaben, beispielsweise die Applikationsbeschleunigung, Analytikberechnungen oder die Virtualisierung. Wenn nur diese Tasks gefragt sind, braucht es die CPU/GPU streng genommen gar nicht. Ein Setting, in dem nur FPGAs zur Verfügung stehen, ist im kommerziellen Umfeld nicht vorhanden.

FPGA für Hyperscaler

Sechs Wissenschaftler von IBM Research Zurich haben sich der Aufgabe angenommen, ein Hyperscalerfähiges System ausschliesslich aus FPGA-Chips zu entwickeln. François Abel, Dionysios Diamantopoulos, Christoph Hagleitner, Mark Lantz, Burkhard Ringlein und Beat Weiss wollten das Potenzial von FPGAs für die ressourcensparende Verarbeitung spezifischer Arbeitslasten in der Cloud nutzen. Die Systeme sollten ausserdem auch für Nicht-FPGA-Experten leicht zugänglich sein. Dabei wurde ein Microservices-Ansatz verfolgt, der es den Anwendern ermöglicht, die Vorteile von FPGAs durch einen API-Aufruf zu nutzen, ohne dass sie etwas über FPGAs wissen müssen oder auch nur zu realisieren, dass ihre Arbeit von einem FPGA ausgeführt wird.

Ausgangspunkt für die Entwicklung der «cloudFPGA» war die Anfrage nach der Cloud-Implementierung mit 1000 FPGAs. Ein System mit Standard-Hardware hätte nicht nur sehr viel teuren Platz im Rechenzentrum eingenommen, sondern auch noch mehrere Millionen Franken gekostet. Die Forscher befanden, dass es eine bessere Lösung geben muss, und machten sich an die Arbeit.

Facebook-Racks als Vorbild

Für das Hardware-Design nahmen sie sich die Hyperscaler zum Vorbild. Facebook, Microsoft & Co. bringen die Chips, Platinen, Speicher, Kühlung etc. auf engstem Raum unter. Die cloudFPGA-Forschungsplattform besteht aus einem 2U-System (zwei Units oder Höheneinheiten) mit zwei Trägerplatinen, in die insgesamt 64 FPGA-Module gesteckt sind, bedeutet: ein FPGA-Modul alle 7,6 Millimeter. Bei einem so geringen Abstand ist kein Platz für Kühlkörper und Lüfter. Stattdessen wurden Kupfer-Wärmespreizer auf die Die des FPGAs montiert, um die Wärme seitlich vom Chip abzuführen. An den beiden Seiten des Wärmespreizers kommt die Abwärme mit zwei Flüssigkeits-Kühlkörpern, den Kühlschienen, in thermischen Kontakt. In den Kühlschienen zirkuliert Wasser, um die von den FPGA-Modulen, dem Ethernet-Switch und den übrigen Steuerungskomponenten erzeugte Wärme zu sammeln und abzuführen.

Bei den FPGA-Modulen handelt es sich nach Angaben der Forscher um ein Xilinx Kintex UltraScale XCKU060. Der Chip mittlerer Leistungsklasse zeichnet sich durch ein sehr gutes Preis-Leistungs-Verhältnis, niedrigen Stromverbrauch und hohe Signalverarbeitungsbandbreite aus. Jede Trägerplatine verbindet die 32 FPGAs über einen Ethernet-Switch (Intel FM6000), der auf die Grösse eines Smartphones geschrumpft wurde, um vertikal in ein 2U-Gehäuse zu passen. Darüber hinaus verfügt jedes der 2U-Systeme über 16 Gigabyte DDR4-Speicher, einen Flash-Speicher für die Konfiguration und einen programmierbaren System-on-Chip-Controller. Mit dem Design von 64 FPGAs in einem 2U-Einschub passen mehr als 1000 FPGAs in ein einziges Rack.